迷你锁相放大器的工作原理与设计优化

更新时间:2025-11-19

浏览次数:412

一、工作原理

锁相放大器(Lock-in Amplifier, LIA)是一种通过相干检测技术提取淹没在强噪声中的微弱周期信号的仪器,其核心思想是利用参考信号与待测信号的相位同步性,通过窄带滤波抑制噪声。迷你锁相放大器是在传统LIA基础上小型化、集成化的设计,适用于便携式测量或嵌入式系统。

1. 基本组成与信号处理流程

迷你LIA的核心模块包括:

输入信号通道:接收待测的微弱周期信号(通常为正弦波、方波等,频率已知或需同步测量)。

参考信号通道:提供与待测信号同频(或倍频/分频)的参考信号(通常为正弦或方波),可能来自外部(如信号发生器)或内部(如通过解调待测信号提取)。

混频器(乘法器):将输入信号与参考信号相乘,将信号频率搬移到直流及高频分量(通过三角函数积化和差公式)。

低通滤波器(LPF):滤除高频分量(通常是参考信号两倍频及以上),保留与参考信号同频的直流分量(即信号幅值与相位的乘积)。

输出模块:输出解调后的直流信号(反映待测信号的幅值和相位信息),通常进一步通过模数转换(ADC)或显示模块呈现。

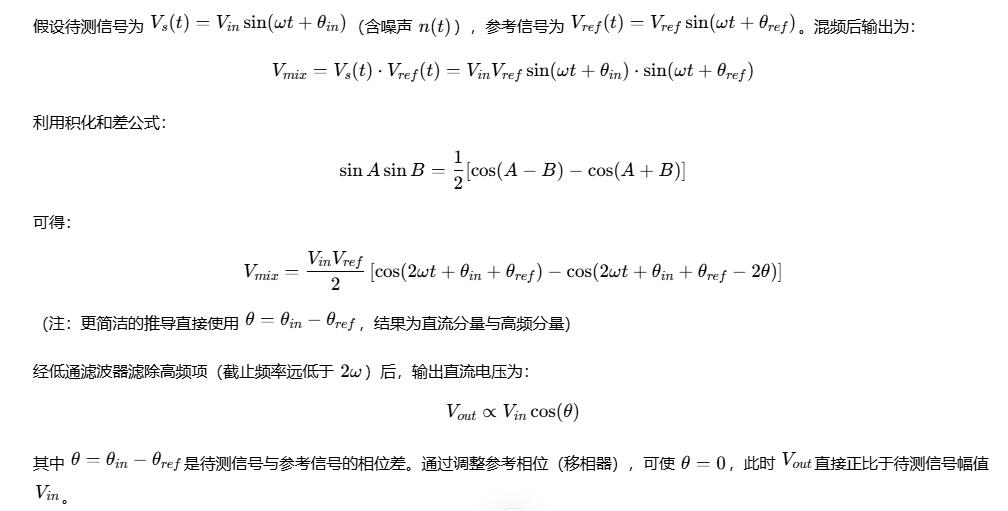

2. 关键数学原理(以正弦参考信号为例)

3. 核心优势:噪声抑制

噪声(如白噪声、环境干扰)通常覆盖宽频带,而待测信号是窄带周期信号。混频后通过低通滤波器仅保留与参考信号同频的直流分量,其他频率的噪声(尤其是非同频成分)被大幅衰减。滤波器的带宽越窄(由低通滤波器的时间常数决定),噪声抑制能力越强,但响应速度会降低。

二、设计优化方向

迷你LIA的设计需在小型化、低功耗、高精度之间平衡,重点优化以下模块:

1. 参考信号源优化

稳定性:参考信号的频率和相位需高度稳定(避免漂移导致解调失效)。可采用晶体振荡器(如TCXO/OCXO)或数字锁相环(PLL)生成精确参考信号。

灵活性:支持外同步(外部参考输入)和内同步(从输入信号提取参考),并允许相位连续调节(0°~360°),以匹配待测信号的相位。

波形选择:正弦参考信号可减少谐波干扰(相比方波),但方波更易生成且通过谐波抑制电路可兼容正弦待测信号。

2. 混频与解调电路优化

模拟乘法器 vs 数字解调:

传统方案使用模拟乘法器(如AD633)进行实时混频,但易受温漂和非线性影响;

现代迷你LIA常采用数字方案(如高速ADC采样后通过DSP/FPGA实现数字混频),精度更高且易于集成。

同步检波:确保参考信号与输入信号的严格同步(通过锁相环锁定参考频率),避免频率失配导致的解调误差。

3. 低通滤波器设计

滤波器类型:常用巴特沃斯或贝塞尔滤波器(保证平坦响应或最小相位失真),阶数越高(如4阶以上),滚降越陡峭(噪声抑制更强)。

截止频率可调:根据待测信号的频率动态调整滤波器时间常数(如通过数控电容或数字滤波算法),平衡噪声抑制与响应速度。

数字滤波替代:在数字方案中,可采用有限冲激响应(FIR)或无限冲激响应(IIR)滤波器,灵活调整截止频率和阶数。

4. 前置放大与抗混叠(针对模拟方案)

低噪声放大器(LNA):输入级采用低噪声运放(如OPA2188,噪声密度<1nV/√Hz),放大微弱信号至合适幅度(避免后续混频饱和)。

抗混叠滤波:若采用ADC采样,需在采样前加入抗混叠滤波器(截止频率为采样率的一半),防止高频噪声混叠到有效频带。

5. 小型化与集成化

芯片级方案:选用集成锁相放大器芯片(如Stanford Research Systems的SR510、ADI的ADL5380+AD8302组合),减少分立元件数量。

模块化设计:将参考源、混频器、滤波器等功能模块集成到单一PCB,通过SMD元件缩小体积(典型迷你LIA尺寸可小于5×5 cm²)。

低功耗设计:采用低静态电流运放和数字芯片(如MSP430或ARM Cortex-M系列),适用于电池供电的便携设备。

6. 相位与幅值校准

自动校准:内置校准电路(如已知幅值的标准信号源),实时补偿增益误差和相位偏移,提升长期稳定性。

双相位解调:同时解调0°和90°相位分量(I/Q解调),可提取信号的实部(幅值)和虚部(相位),适用于复数信号分析。

三、典型应用场景

迷你锁相放大器因其高灵敏度和抗噪能力,广泛应用于:

微弱信号检测:如光电探测器信号(光电流)、生物电信号(神经元放电)、材料科学中的阻抗谱测量(如电化学阻抗)。

科研与教学:便携式实验设备(如大学物理实验中的光调制测量)。

工业检测:传感器信号解调(如光纤传感、应变片测量)。

四、总结

迷你锁相放大器的核心是通过相干检测将微弱周期信号从噪声中提取出来,其设计优化的关键在于:高稳定性的参考信号源、低噪声的前置放大、精确的混频与滤波(模拟或数字方案),以及小型化集成。随着数字信号处理技术的发展,基于FPGA/DSP的数字锁相放大器逐渐成为主流,在保持高性能的同时显著降低了体积和成本。